## **Tutorial 7 Questions (Part 2)**

## **Introduction to Verilog**

Please try out these self-study questions (labeled "SS"). These will not be discussed in class and solutions will be provided later.

Please refer to the self-study Verilog MCQ questions on Luminus.

## **Verilog Modeling**

Check that the syntax of your programs is correct by using the Xilinx tool!

1. Data encryption schemes are commonly used to secure data privacy. Write a Verilog program for a *digital decrypter* which has a 5-bit input, DATA\_IN of the form "C<sub>2</sub>O<sub>1</sub>C<sub>1</sub>O<sub>0</sub>C<sub>0</sub>" where the operation applied to the three bit data "C<sub>2</sub>C<sub>1</sub>C<sub>0</sub>" to produce the 3-bit output DATA\_OUT depends on the two bits "O<sub>1</sub>O<sub>0</sub>" as shown in the table below.

| "O <sub>1</sub> O <sub>0</sub> " | DATA_OUT                                         |  |  |

|----------------------------------|--------------------------------------------------|--|--|

| "00"                             | "C <sub>2</sub> C <sub>1</sub> C <sub>0</sub> "  |  |  |

| "01"                             | $C_0C_2C_1$                                      |  |  |

| "10"                             | "C <sub>1</sub> C <sub>0</sub> C <sub>2</sub> "  |  |  |

| "11"                             | " $\overline{C}_2\overline{C}_1\overline{C}_0$ " |  |  |

2. A machine receives two 3-bit unsigned inputs **X**, **Y** and outputs a 6-bit unsigned output **Z** where **Z** is the product of **X** and **Y**. Write a Verilog program that implements this machine without using the multiplication operator.

*Hint: Use the shift and add method to perform multiplication i.e.*

## **Digital Fundamentals**

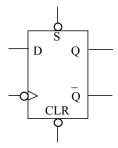

3. The 74'74B is an integrated circuit containing negative-edge triggered D flip-flops with synchronous set and asynchronous reset inputs. The D flip-flop receives four 1-bit input signals, **D**, **CLK**, **S**, **CLR** and produces two 1-bit output signals, **Q** and **QB**. Write a Verilog program that implements the D flip-flop according to the characteristic table shown below.

| CLK          | CLR | S | D | Q⁺ |

|--------------|-----|---|---|----|

| Х            | 0   | Χ | Χ | 0  |

| <b>\</b>     | 1   | 0 | Χ | 1  |

| $\downarrow$ | 1   | 1 | 0 | 0  |

| $\downarrow$ | 1   | 1 | 1 | 1  |

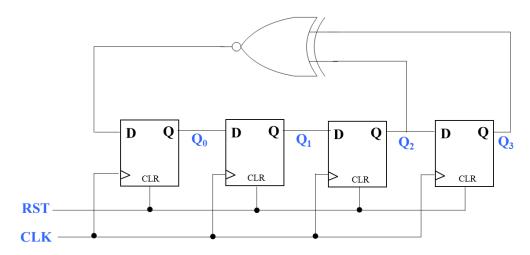

4. The circuit as shown below is a linear feedback shift register (LFSR) where the input bit to the chain of FFs is a function of its previous output. LFSRs are able to generate pseudorandom bit sequences which have applications in cryptography, bit-error-rate measurements to wireless communication systems.

The LFSR below receives two 1-bit inputs, CLK and RST and generates a 4-bit output Q. The RST signal sets the output of the LFSR to 4'b000 asynchronously when enabled.

The D flip-flops used are positive-edge triggered with asynchronous active high clear.

Write a Verilog program that implements the LFSR according to the circuit above. Simulate / work out the operation of the circuit to work out the bit sequence of Q.